まずシフトレジスタとは、FF(フリップフロップ)を複数用いて値を右から左へ、または左から右へシフトさせるものです。よく使われる場面として、直列並列変換(シリアルパラレル変換)があるかなと思います。

具体的にどういったものかは、言葉で書くよりタイミングチャートで示したほうがわかりやすいかと思うので下記にまとめていきます。

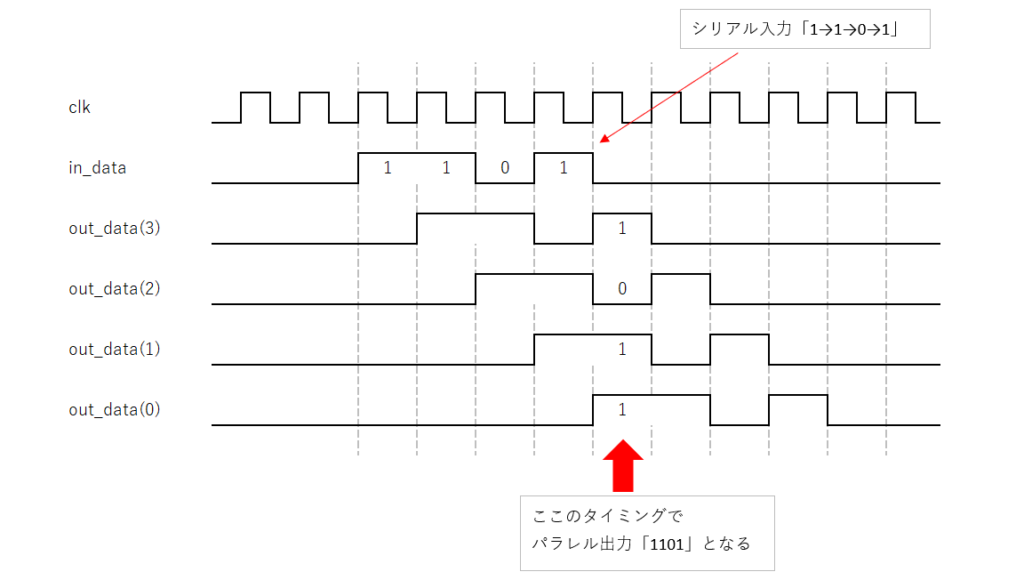

1. シフトレジスタのタイミングチャート

例として直列並列変換でシフトレジスタの動きをみていこうと思います。

「1 → 1 → 0 → 1」というシリアル入力(直列入力)があったときに、「1101」と4bitのパラレル(並列)に変換されて出力されるときのタイミングチャートが下記になります。

タイミングチャートからもわかるようにシリアル入力されてから4クロック後にパラレル変換が完了します。

このときのout_data(0)~out_data(3)がパラレル変換後の4bitのバス幅をもった出力ということになります。

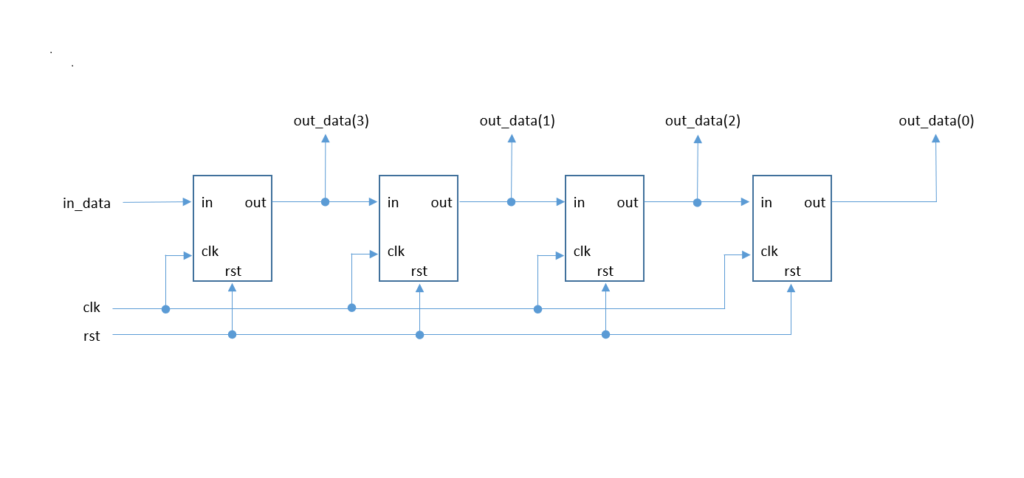

2. 構成

シリアルパラレル変換の構成は単純で、タイミングチャートからもわかるように4つのFFのみで構成されます。

回路図をしたに描いてみます。

3. verilogHDL, VHDLでの記述法

最後に、同期シリアルパラレル変換をverilogHDL,VHDLそれぞれでの記載例をまとめておきます。

※entityなどの宣言等は省略し、信号宣言と機能ブロックのみまとめます。

verilogHDLでの記述例

input clk, rst;

input in_data;

output [3:0] out_data;

reg [3:0] out_data;

always @(posedge clk) begin

if (rst == 1’b1) begin

out_data <= 4’b0000;

end

else begin

out_data <= {out_data[2:0],in_data};

end

end

VHDLでの記述例

clk : in std_logic;

rst : in std_logic;

in_data : in std_logic_vector (3 downto 0);

out_data : out std_logic_vector;

signal reg_data : std_logic_vector (3 downto 0);

process ( clk )

begin

if (rst = ‘1’) then

reg_data <= ( others => ‘0’ );

else

reg_data <= reg_data(2 downto 0) & in_data;

end if;

out_data <= reg_data;

end process;

上記にverilogとVHDL、それぞれの記述例をまとめてみました。他にも様々な記述方法がありますが、個人的には連接演算子を用いた書き方が最もシンプルでわかりやすいかなと思っています。

動きはタイミングチャートにかいたとおりに、毎クロックの立ち上がりでout_data(VHDLではreg_data)の下位3bitに入力のin_dataが右側に連接(最下位bitに付加)されます。

結果的に、in_dataを付加して元のデータを左側に1bitシフトした形になります。(元のデータの最上位bitは無くなる)

また、特定の入力値のみを取り込みシフトさせたいときは、イネーブル信号を追加することでイネーブル付きシフトレジスタとなります。

コメント