4-2セレクタとは、入力が4つあり、出力が2つあるセレクタのこと。

今回は、入力が2bitの信号四本と、1bitの制御信号2本、1bitの出力2本を例にして、その真理値表と回路図の一部、条件演算子を用いたverilogでの記述法をメモしておきます。

入力 : A, B, C, D [1:0]←2ビットを表す

選択信号 : SEL1, SEL2

出力 : OUT1, OUT2

A0はAの1bit目、A1はAの2bit目を表しています。

| SEL1 | SEL2 | OUT1 | OUT2 |

| 0 | 0 | A0 | A1 |

| 0 | 1 | B0 | B1 |

| 1 | 0 | C0 | C1 |

| 1 | 1 | D0 | D1 |

表からもわかるように、SEL1とSEL2がともに0の時は、OUT1にA0、OUT2にA1が出力されます。今回は選択信号が合計2bitしかないので4パターンですが、3bit4bitと増やすと出力のパターンも増やすことができます。

上の表を論理式で表すと

となります。

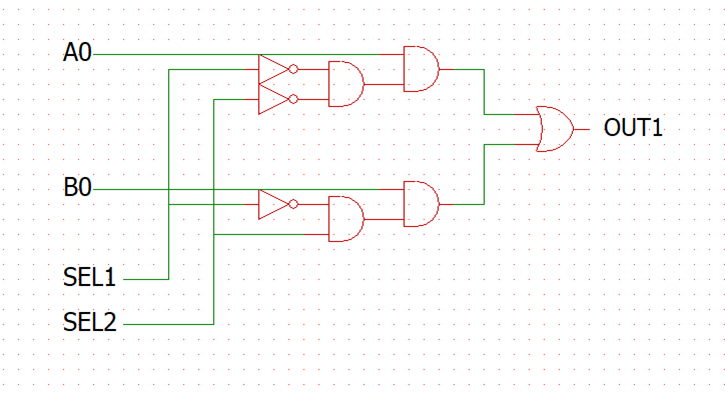

回路図でその一部を表してみると

上記の回路図は、A0とB0についてしか描いていませんが、他のも同様に描けば大丈夫です。

4-2セレクタを条件演算子を使って書くと下記のようになります。

input [1:0]A,B,C,D;

input SEL1, SEL2;

output OUT1, OUT2;

assign OUT1 = SEL1 == 0? ( SEL2 == 0? : A0 : B0) : ( SEL2 == 0? : C0 : D0);

assign OUT2 = SEL1 == 0? ( SEL2 == 0? : A1 : B1) : ( SEL2 == 0? : C1 : D1);

コメント